### **DECEMBER** 2016

www.edn-europe.com

europe

### THE WORLD'S LARGEST SELECTION OF ELECTRONIC COMPONENTS **AVAILABLE FOR IMMEDIATE SHIPMENT**

bel

FIND CONTACT AND ORDERING INFORMATION FOR YOUR REGION AT

**NOW** more than **5 MILLION PRODUCTS** from over 650 SUPPLIERS

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2016 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

RECOM

SEMTECH

#### COVER

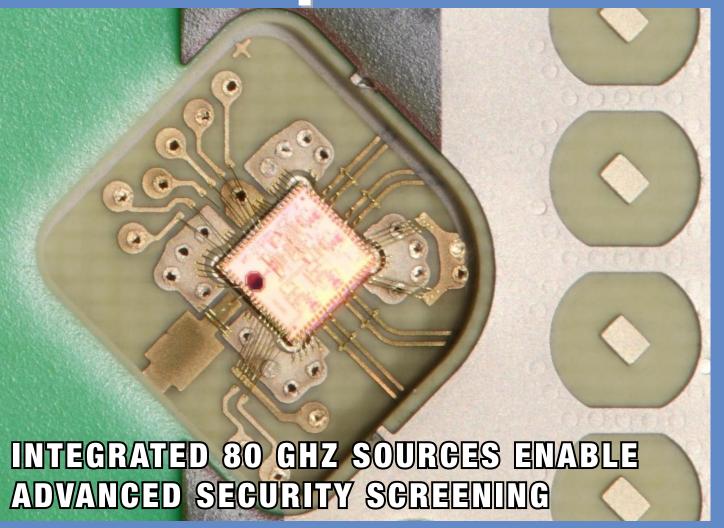

# Millimetre wave expertise enables faster, more efficient security screening

If you are travelling by air in the coming holiday season, you may find yourself being security scanned using mmWave techniques. Rohde & Schwarz - that readers of these pages usually know better as a test & measurement or RF communications provider - recently entered this market with a design that the company says represents a marked step forward from existing products in the security market. EDN Europe invited R & S to provide some insight as to how the company's RF and T&M experience has been applied to this use of mmWave technology. You can read more in the article on page 17

#### **FEATUREARTICLES**

- 17 Airport security screening with millimetre waves

- by Dr. Sherif Sayed Ahmed, Rohde & Schwarz

- 20 Optimized for ADAS applications: new compiler challenges – part 2 by Dr. Alexander Herz, Tasking

- 23 How GaN is transforming RF energy and cooking applications by Mike Ziehl and Mark Murphy, MACOM

- 27 Low cost and low drop-out linear and switched-mode supercap chargers by Dan Tooth, Texas Instruments

- 29 Avoiding the ASIC vs FPGA gamble; smart engineering requires smart SoC design

by Patrick Osterloh, Toshiba Electronics Europe

#### **ONLINE THIS MONTH**

New Multiplier-Accumulator accelerates polynomials

New possibilities for smart-factory security

Understanding and designing differential filters for communications systems

#### **EDN's columns**

- 4 EDN.comment M&A, or, Let's buy something!

- 6 Pulse

Automatic parallelisation research promises faster code; 3rd-generation silicon carbide technology; Microsemi offers open RISC-V core in FPGA; Cortex-M4 ultra-low-power MCUs; Xilinx dynamic reconfiguration offers compute efficiency gains; Electric-vehicle wireless battery management; Wolfspeed sponsors access to RF Tutorial series; 12-48V, 6-phase, bidirectional DC/DC controller for dual-rail automotive; Ubuntu Core 16 for secure IoT; 100A, small-package current sensor ICs; Clinical-grade ±0.1°C temperature sensor; MEMS-based RF switches from ADI; 4x 120A dual-phase DC/DCs for 480A output; Programmable mixed-signal ICs add PMIC functions

- 19 Analog Tips ADC input impedance matching by lan Beavers

- 25 Embedded Systems7 tips for optimizing embedded softwareby Jacob Beningo

- **41 Tales from the Cube** The chip glitch

- 37 Product Roundup

AEC-Q100-Qualified 8-bit MCUs; Sub-1-GHz, ultra-low-power ISM-band transceiver; e-paper starter kit; Arduino-compatible shield for stepper designs; RISC-V SoC analysis and debug; IR sensor array for low-res thermal imaging; 16-bit current measuring module; 24 GHz radar module; 5in. format Arduino-compatible touch-display; Cypress/Broadcom IoT multi-protocol wireless development; Over-the-air power measurement to 75 GHz; 14-bit PXI oscilloscope; Intelligent motion-control SiP hosts STM32; Intel Joule IoT apps development platform; Prototype 'mid-air touch' controls; Ultra-small platform for wearable developments

- 32 Design Ideas

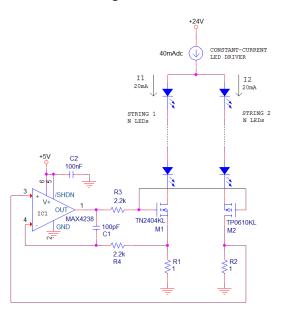

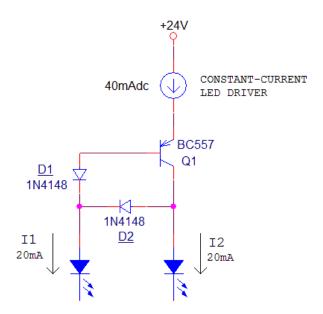

- 32 LED strings driven by current source/mirror

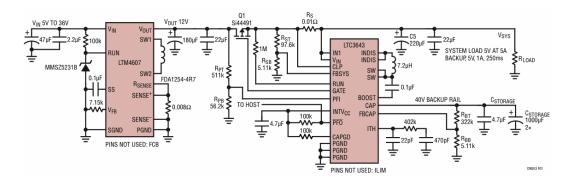

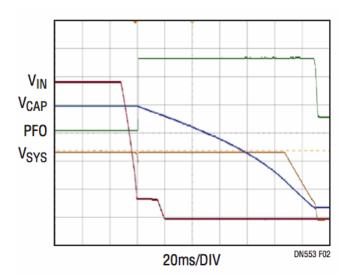

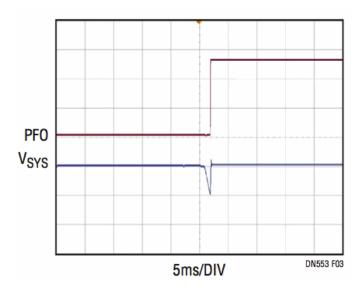

- 33 LTC Design Note: Electrolytic capacitor-based data backup power solution for a 12V system with 5V to 36V input

**EDN Europe** December 2016

as 2016 comes to a close, there can be no doubt that one of the phenomena that has marked it out has been the seemingly endless stream of takeovers in the electronics industry. The activity is generically labelled M&A, mergers and acquisitions, but few of this year's deals have been in any real sense mergers. Straightforward acquisitions have been the predominant model.

The driving forces behind the trend are easy to identify; economies across the world are marking time, with limited opportunities for "organic" growth. There is no shortage of unemployed capital looking for something to do; money is cheap. Managements - not only in the semiconductor/electronics sector - are under shareholder pressure to improve results and if you can't readily grow the numbers by internal growth, then boosting turnover by a corporate transplant is an obvious option. For companies fortunate enough, or well-managed enough, to have their own cash reserves, these are not good times for the cash-at-bank line on the balance sheet. In an era of minimal or even negative interest rates, there is a need to get that money working.

There are too many such deals to revisit many of them them here; but they have touched the IP business (ARM to Softbank, July); semiconductors both integrated (NXP to Qualcomm, October) and fabless (Lattice to Chinese owners, November); and the distribution

#### M&A, OR, LET'S BUY SOMETHING!

sector (Premier Farnell to Avnet, July). Executing successful acquisitions is a very difficult process. Estimates vary, but when analysts pronounce on what proportion of large-company M&A exercises end up with a clearly positive outcome, the percentages are not high. Very early in the typical acquisition announcement, the term "synergy" will appear. Synergy is a word I try to avoid. If I do use it, I will intend the sense to be the potential for activities to combine harmoniously to yield an overall outcome that is more than the sum of the parts. One plus one yields more than two. In the typical M&A press statement, "synergy" has come to mean the opportunities to eliminate overlap in corporate functions (which means people) to reduce the combined business' costs. Which leads directly to one of the classic M&A problems; you embark on a path that is intended to be about adding and growing, but your immediate focus and mindset has to be on cutting and shrinking.

The hazards of the M&A process are many, far too many to work through here. But 2016's crop of deals has demonstrated most of them. At the most basic level, for staff of the acquired and acquiring companies, is the question, "Do I still have a job?" And, "if I do, am I going to enjoy working here any longer?" For example, I have rarely heard executives of an acquired company so openly apprehensive as in one interview I conducted this year, "We have always had a

simple management structure, only three layers: they [the acquiring company] have at least twice that. How is that going to work?" From such seemingly minor concerns, much heartache can flow.

On the customer side – that's you, reading this column – there is the worry, "Will the product line that my project depends on, be a casualty of this merger? Even if it's still on the combined company's catalogue, will it have the same level of support?" Thus – again, just one example – the electronica trade show saw Microchip (bought Atmel, January) energetically broadcasting the message, "Yes! We definitely are going forward with both microcontroller architectures [PIC and AVR]"

Part of the organic process that has shaped the industry we know, is exactly the fact that some of these deals work out, and some don't. Occasionally you can look back at the outcome of such a merger and see a dynamic entity expanding into new territory that its constituent parts might not have reached. But perhaps not often. Product lines, technologies, divisions and most importantly, people, will be scattered to new homes as part of the continuing fall-out. And – to close on a more positive note – some of those will be part of the next crop of technology innovators.

graham.prophet@eetimes.be

# OUSE

#### Automatic parallelisation research promises faster code by non-experts

esearchers at MIT have reported work that they say will allow non-specialists - that is, not specialised in the process of manually coding parallel execution of program flow - to optimize programs that run on, and make best use of, multiprocessor chips. Dynamic programming - says the MIT information release - is a technique that can yield relatively efficient solutions to computational problems in economics. genomic analysis, and other fields. But adapting it to computer chips with multiple cores requires a level of programming expertise that few (for example) economists and biologists have.

In experiments, the researchers used the system to "parallelize" several algorithms that used dynamic programming, splitting them up so that they would run on multicore chips. The resulting programs were between three and 11 times as fast as those produced by earlier techniques for automatic parallelization, and they were generally as efficient as those that

were hand-parallelized by computer scientists.

Dynamic programming offers exponential speedups on a certain class of problems because it stores and reuses the results of computations, rather than recomputing them every time they're required.

"But you need more memory, because you store the results of intermediate computations," says Shachar Itzhaky, first author on the new paper and a postdoc

in the group of Armando Solar-Lezama, an associate professor of electrical engineering and computer science at MIT. "When you come to implement it, you realize that you don't get as much speedup as you thought you would, because the memory is slow. When you store and fetch, of course, it's

still faster than redoing the computation, but it's not as fast as it could have been."

Computer scientists avoid this problem by reordering computations so that those requiring a particular stored value are executed in sequence, minimizing the number of times that the value has

> to be recalled from memory. That's relatively easy to do with a single-core computer, but with multicore computers, when multiple cores are sharing data stored at multiple

locations, memory management become much more complex. A hand-optimized, parallel version of a dynamic-programming algorithm is typically 10 times as long as the single-core version, and the individual lines of code are also more complex.

The CSAIL researchers' new

system - dubbed Bellmania. after Richard Bellman, the applied mathematician who pioneered dynamic programming — adopts a parallelization strategy called recursive divide-and-conquer. Suppose that the task of a parallel algorithm is to perform a sequence of computations on a matrix. Its first task might be to divide the matrix into four parts, each to be processed separately. But then it might divide each of those four parts into four parts, and each of those into another four parts, and so on. Because this approach recursion — involves breaking a problem into smaller subproblems. it naturally lends itself to parallelization.

With Bellmania, the user simply has to describe the first step of the process — the division of the matrix and the procedures to be applied to the resulting segments. Bellmania then determines how to continue subdividing the problem so as to use Complete memory efficiently.

#### 3rd-generation silicon carbide tech in FETs, SBDs and modules

ohm Semiconductor is now fabricating devices in a 3rd generation of SiC technology, for MOSFETs, SiC Schottky Barrier Diodes (SBDs) and SiC modules. Rohm says it is now mass-producing the first trench-type SiC MOSFETs. This generation of SiC MOSFETs reduces on-resistance by 50% across the entire temperature range and input capacitance by 35% in the same chip size compared with planar gate-type SiC MOSFETs. This also makes it possible to reduce the size of peripheral components such as

coils and capacitors by increas-

ing switching frequency. The new SCT3080KL 1200V SiC **MOSFET** series in a TO-247 package is an example. 650V FETs in that package are

available with 120 m $\Omega$  down to 17 mΩ on-resistance; at 1200V the range spans 160 to 22 m $\Omega$ . Rohm will also offer an AECQ qualified SiC MOSFET based on its 2nd

Gen planar series.

temperature range among all of the SiC SBDs currently available. Rohm claims. In addition to this, they feature high surge current capability for power supply applications. Adding to the recently announced TO220AC devices at 650V/6. 8 and 10A. Rohm has introduced D2PAK and TO220FM devices also adding lower current options, 2A and 4A to the family. Full SiC modules include chopper type modules for converters and integrate both trench SiC MOSFETs and SiC SBDs. In addition to 2 in 1 type modules, 1200V/120A,180A and 300A Chopper type modules are being prepared. Rohm adds that it is working on a new power module which will exhibit

lower stray inductance.

#### Microsemi offers open RISC-V core, in FPGA, for embedded designs

icrosemi has announced that its FPGA devices can be configured with a processor core in the Open RISC-V Architecture: the offering comprises an IP core and comprehensive software solution for embedded designs and will be implemented on IGLOO2. SmartFusion2 and RTG4 devices. Microsemi says it is the first field

programmable gate array (FPGA) provider to offer a comprehensive

software tool chain and intellectual property (IP) core for RISC-V designs. The

RISC-V

company's RV32IM RISC-V core is

available for Microsemi's IGLOO2 FPGAs, SmartFusion2 system-on-

chip (SoC) FPGAs or RTG4 (radiation-tolerant) FPGAs, with an Eclipsebased Soft-

Console integrated development

environment (IDE) hosted on a Linux platform and the Libero SoC Design Suite providing full design support.

Microsemi's RV32IM RISC-V core. developed in collaboration with Si-Five, enables engineers to design with an open instruction set architecture (ISA), enabling complete portability and a more secure pro-

### oulse

cessor architecture governed by a permissive BSD license. RISC-V is an ISA which is now a standard open architecture under the governance of the RISC-V Foundation. RISC-V offers, Microsemi says, a 'compelling' soft processor solution for low power, reliable, secure FPGAs, "Now engineers can rely on an open ISA, without

being tied to a single vendor and make use of open source tools and hardware. Never before has a processor allowed designers to inspect, modify, adapt, collaborate and migrate their design to the best platform for their product." The Libero SoC Design Suite is ready to implement the IP and, Microsemi adds, will efficiently

pack [the core into] the FPGA logic elements (LEs), vielding a cost-effective solution. The Eclipse-based SoftConsole IDE running on Linux allows users to compile and debug their source code. For applications such as safety and security, the register transfer level (RTL) source code is available for inspection; customers

can verify the security of the processor themselves, which is not possible with other processors, as they have closed architectures. In safety-critical applications, as customers can run multiple RISC-V cores to ensure if one fails, there is a redundant core **Complete** to take over.

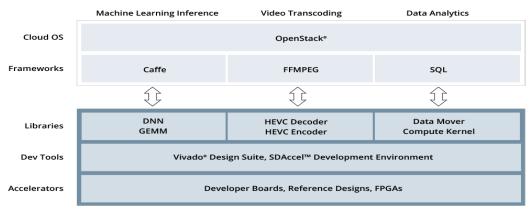

#### Xilinx dynamic reconfiguration offers compute efficiency gains

ntended to accelerate mainstream adoption of Xilinx FPGAs in hyperscale data centres, the company has disclosed technology designed to enable the world's largest cloud service providers (and offered, at present, only to them) to rapidly develop and deploy acceleration platforms. Designed for cloud scale applications, the FPGA-powered Xilinx Reconfigurable Acceleration Stack includes libraries, framework integrations, developer boards, and OpenStack support. It provides the fastest path to realize 40x better compute efficiency with Xilinx FPGAs compared to x86 server

CPUs and up to six times the compute efficiency over competitive FPGAs. Using dynamic reconfiguration, Xilinx enables silicon optimization for the broadest set of performance-demanding work-

loads including machine learning. data analytics, and video transcoding. These workload optimizations can be done in milliseconds by swapping in the most optimal design bitstream. Xilinx attributes

Xilinx Reconfigurable Acceleration Stack

the 2-6x gain in compute efficiency in machine learning inference to DSP architectural advantages for limited precision data types, and greater on-chip memory resources.

The Xilinx Reconfigurable Acceleration Stack includes math libraries designed for cloud computing workloads, application libraries integrated with major frameworks, such as Caffe for machine learning, a PCle-based development board and reference design for high density servers, and an OpenStack support package making Xilinx FPGA-based accelerators easy to provision and manage. Complete

#### Cortex-M4 ultra-low-power MCUs for wearables, from Maxim

Maxim configured the MAX32630 and MAX32631 ARM Cortex-M4F-based microcontrollers to provide fast processing in a tiny package, while extending battery life, for designs including high-performance fitness and medical/wearable devices.

The MCUs' power management maximizes run time and provides the lowest energy consumption, in active (127  $\mu$ W/MHz), DMA (32  $\mu$ W/MHz), and retention sleep (3.5  $\mu$ W) modes. The microcontrollers offer ample onboard code (2 MB flash), data (512 kB SRAM), and cache (8 kB) memory, to run third-party applications and logging sensor data. Interfaces include SPI, SPI XIP, UART, I<sup>2</sup>C, 1-Wire, and USB ports. Peripheral functions include six 32-bit tim-

ers, clock, 66 general-purpose I/O pins, pulse train engine, and 10-bit analogue/digital converter (7.8 ksamples/sec) The MAX32631 adds a trust protection unit (TPU) that enables advanced hardware encryption and authentication features, providing customers with a complete security toolbox to protect IP, algorithms, and user data. The MAX32630 and secure

MAX32631 are based on the Cortex-M4F 32-bit microcontroller core with floating-point unit, and are packaged in a 4.37 × 4.37 mm 100-ball WLP package. An evaluation kit is available: MAX32630-EVKIT, with pricing starting at \$150.00. MAX32630 pricing starts at \$6.66 (1000).

#### Linear Technology demos electric-vehicle wireless battery management

WITEESS BMS

t the electronica 2016 exhbition, Linear Technology featured a BMW i3 'concept car' in which the internal communications between battery management PCBs within the main traction battery pack are implemented by wireless links, using its own Dust Networks 2.4 GHz mesh networking.

The wireless BMS concept car, developed by Linear's design partner LION Smart, combines Linear's highly accurate battery stack monitors with its SmartMesh wireless mesh networking, replacing the conventional wired connections between the battery packs and the battery management system. Benefits, Linear says,

include the potential for improved reliability, lower cost and weight, and reduced wiring complexity for

large multicell battery stacks for electric and hybrid/electric vehicles.

The demonstration also uses battery packs from Kreisel Electric, specialists in maximising the performance of 18650 cylindrical cells; the company builds battery

packs that are liquid cooled, and heated, with a system integrated with the car's HVAC system. Opti-

mum charging, the collaborating companies explain, can only take place when the battery pack is at a constant 30C, and heating as well as cooling may be required. The partners claim that given sufficient available power, charging to 80% in 18 minutes is feasible.

Linear presents its high voltage battery stack monitors as offering leading accuracy and reliability, enabling battery management systems that maximize battery pack performance and longevity. The LTC6811 is a complete battery measuring device for hybrid/electric vehicles that can measure up to 12 series-connected bat-

# pulse

tery cell voltages with better than 0.04% accuracy. Combining the LTC6811 with Linear's SmartMesh wireless mesh networking system

addresses concerns associated with automotive wiring harnesses and connectors.

The wireless BMS concept car,

Linear says, shows the promise of wireless technology to significantly improve reliability and simplify the design of automotive battery management systems.

#### Wolfspeed offers free access to RF Tutorial series

olfspeed, supplier of gallium nitride on silicon carbide (GaN-on-SiC) high electron mobility transistors (HEMTs) and monolithic microwave integrated circuits (MMICs), is sponsoring one year of free access to a comprehensive multimedia engineering tutorial on passive and active RF circuits, including amplifiers. Entitled "Conquer Radio Frequency: A Multimedia Conceptual Guide to RF & Microwave Engineering, Based on AWR Microwave Office Video Tutorials," the tutorial was written by Dr. Francesco Fornetti, a noted expert in advanced semiconductor materials and devices, including

GaN HEMTs.

The online tutorial provides users with a full-colour reference textbook that serves as an introduction to the fundamental principles of both passive and active RF and microwave circuit design. In the more than 12 hours of circuit design video tutorials that accompany the textbook, Dr. Fornetti illustrates how to design, test, and characterize RF power amplifiers using the proprietary large signal GaN HEMT models that Wolfspeed developed for the NI (National Instruments) AWR Design **Environment Microwave Office** suite of design tools.

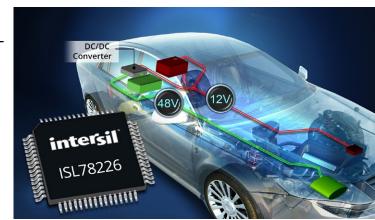

#### 12-48V, 6-phase, bidirectional DC/DC controller for dual-rail automotive

ntersil's ISL78226 is a bi-directional power conversion controller that is designed for 12V to 48V interconnection in hybrid cars and other vehicles.

The device is a 6-phase synchronous PWM controller that performs buck and boost conversion between buses. A single controller can deliver up to 3.75 kW with conversion efficiency of greater

than 95%, and can interleave in a modular master/slave architecture (up to four chips) to achieve higher powers. 48V is appearing in more designs, Intersil says; it is more effective at delivering power to the road, and offers better regenerative braking. Alternators – in fact a starter/generator - in mixed architectures will be at 48V, so generating the 12V rail is a buck opera-

tion. Many functions that are now mechanically or hydraulically driven will be electrified; for example, oil pumps and electric turbochargers.

The ISL78226 eliminates the complexity of earlier designs, Intersil says. It re-

sponds to changing load requirements by dropping phases and can handle abrupt load changes. It has a PMBus interface, and internal limp-home mode. The chip can remove much of the complex-

ity associated with design of a 48V 'mild hybrid', Intersil adds. The device is AEC-Q100 Grade-1

qualified for -40 to +125C operation.

#### **Ubuntu Core 16 delivers foundation for secure IoT**

anonical – the company that is the commercial face of Ubuntu - has issued Ubuntu Core 16 for the Internet of Things (IoT), with regular and reliable security updates, and app stores for intelligent connected devices. Ubuntu Core is a tiny, transactional version of Ubuntu for IoT devices and large container deployments. It runs a new breed of super-secure, remotely upgradeable Linux app packages known as snaps. Major features of the package include; snap confinement ensures applications are trusted only with necessary data; the code meets industry and regulatory require-

ments for updates, operations and security; and provides mechanisms for ISV, manufacturer and enterprise control of updates. The Ubuntu Core promises 'aroundbreaking' security, management, operations and upgradability in a compact, developerfriendly platform, thanks to its use of 'snap' packages. Snaps are securely confined, read-only, tamper-proof application images, digitally signed to the integrity of IoT software. Update Control allows software publishers and manufacturers to validate updates across the ecosystem before they are applied. Snap updates are

transactional, which means that failures are automatically rolled back, giving developers the confidence to update their applications regularly.

The operating system and kernel in Ubuntu Core are also delivered as snaps, so the entire platform is transactionally upgradeable. All Ubuntu Core devices, from all manufacturers, will have free, regular and reliable OS security updates. "Ubuntu Core secures the Internet of Things and provides an app store for every device," said Mark Shuttleworth, founder of Ubuntu and Canonical.

The universal or device-specific

snap app store supports developers throughout the device lifecycle from beta testing to general availability, allowing them to sell loT software as easily as cloud, enterprise and mobile software. A white label app store helps device manufacturers build a branded, differentiated device and software experience.

Complete article, here

#### Precision voltage reference drives up to 200mA, stable vs load

inear Technology is calling its latest IC a "refulator" as it combines the functions of voltage reference and voltage regulator; LT6658 is a precision voltage reference that incorporates two high current output buffers. Based on a 2.5V bandgap voltage reference, each output can be separately configured for any voltage between 2.5V and 6V. Both outputs offer 0.05% initial accuracy, 10ppm/°C temperature drift and 1.5ppm of low frequency noise.

# pulse

The device's outputs can drive up to 50 mA and 150 mA, respectively, and sink up to 20 mA. Typical load regulation is 0.1ppm/mA with up to 150 mA of load current. In parallel, the buffer outputs can be combined for even higher current capability. LT6658 is suitable for driving the reference input for a high resolution ADC or DAC us-

ing one output, while simultaneously supplying power to other devices using the second output. Both outputs track each other over temperature and

load, allowing them to address applications requiring ratiometric supply rails. The outputs have excellent supply rejection and are stable with up to 50 µF

over the entire specified operating range. With this output capability, the LT6658 can serve as both reference and regulator combined. Alternatively, the LT6658 can be used to generate a reference plus a virtual ground, or as two matched, tracking references.

#### 100A, small-package current sensor ICs, with precision programming

llegro MicroSystems' ACS780/ACS781 are fully integrated current sensor linear ICs in a core-less package designed to sense AC and DC currents up to 100A. This automotive-grade. low-profile (1.5 mm thick) sensor IC package represents the highest current density of any Allegro current sensor IC package to date. This package has a very small footprint and delivers extremely high power density for current sensing applications. The Hall sensor technology also incorporates common-mode field rejection to optimise performance in the presence of interfering mag-

netic fields generated by nearby current-carrying conductors.

The devices consist of a precision, low-offset linear Hall circuit with a copper conduction path located near the die. Chopperstabilized

signal path and digital temperature compensation technology also contribute to the stability of the devices across the operating temperature range. High-level immunity to current conductor dV/dt and stray electric fields is offered

The internal resistance of this conductive path is typically 200  $\mu\Omega$ , providing low power loss. The thickness of the copper conductor allows survival of the devices at

high overcurrent conditions. The terminals of the conductive path are electrically isolated from the signal leads allowing the device to operate safely with voltages up to 100V peak on the primary conductor.

These sensor ICs are suited for automotive, industrial and computer applications. Automotive applications include EPS and DC/DC converters and oil and HVAC pumps that require higher currents. Industrial applications include low side sensing in VFD and other motor control systems.

#### Clinical-grade human body temperature sensor has ±0.1°C accuracy

TO I2C

axim Integrated has posted details of the MAX30205 temperature sensor for thermometer applications. The sensor accurately measures temperature and provides an overtemperature alarm/interrupt/shutdown output. The chip converts the temperature measurements to digital form using a high-resolution, sigma-delta, ADC. Accuracy meets clinical

thermometry specification of the

ASTM E1112 when soldered on the final PCB. Communication is through an I<sup>2</sup>C-compatible 2-wire serial interface that accepts stan-

dard write byte, read byte, send

+2.7V TO +3.3V

MAX30205

byte, and receive byte commands to read the temperature data and configure the behaviour of the opendrain over-

long-range,

two-way

global IoT

resulting in

a low-cost,

low-power

device-to-

cloud con-

nectivity

solution.

The prod-

network

temperature shutdown output. The MAX30205 features three address select lines with a total of 32 available addresses. The sensor has a 2.7V to 3.3V supply voltage range, 600 µA supply current, and a lockup-protected I<sup>2</sup>C-compatible interface for wearable fitness and medical applications.

#### Sigfox FCC-certified long-range RF transceiver from Microchip

icrochip claims the first FCC-certified – certified also for use in Europe – fully integrated RF transceiver and kits for developing IoT solutions for use on the Sigfox network; the ready-to-run package offers easy connectivity and low-power consumption for devices running on Sigfox's dedicated IoT network.

The ATA8520E transceiver is the first fully Sigfox-certified chip for North America and Europe and is supported by a standalone evaluation kit and Xplained PRO de-

velopment boards. It hosts Microchip's highly integrated ATA8520E, a lowpower RF transceiver with an integrated AVR micro-

controller. The kits contain the first FCC-certified board that allows developers to connect to Sigfox's

uct is available in two versions. Customers can either purchase Microchip's Sigfox-certified ATA8520-EK as a standalone kit, designed primarily to test the technology, or as a kit combined with an Xplained PRO board for system-design purposes. Both are dedicated for Sigfox's IoT network in the licence-free ISM bands. The solutions come complete with the Sigfox library, modulation, ID and PAC code, and a security key enabling IoT developers to help get their design to market. Sigfox is currently operating in 24 countries and registering over 8 million devices in its network.

Complete article, here

#### MEMS-based RF switches now a 'commercial reality' says ADI

nalog Devices has introduced RF switch technology capable of 14 GHz operation, using chipscale switching elements – MEMS switches – that it is initially aiming at markets such as test & measurement, to replace electromechanical relays. This will, ADI says, enable next-generation instrumentation equipment with increased channel density and extended speed, operating lifetime and reduced power consumption. The first in a new product series, ADI's ADGM1304 and ADGM1004

RF MEMS switches are presented

as 95% smaller, 30 times faster, 10 times more reliable, and use 10 times less power than conventional electromechanical relays. Future products

within the MEMS switch series will replace relays in aerospace and defence, healthcare, and communications infrastructure equipment, allowing OEMs in those markets

ADGM1304

to pass similar size, power and cost savings along to their customers.

Unlike other switch alternatives such as solid-state relays, the

ADGM1304 and ADGM1004 MEMS switches have superior precision and RF performance from 0 Hz (DC) to 14 GHz. ADI's MEMS switch solution contains two dice to maximize operational performance – an electrostatically actuated switch in a hermetically sealed silicon cap, and a low-voltage, low-current driver IC. The switching element has a highly conditioned, extremely reliable metal-to-metal contact that is actuated via an electrostatic force generated by the companion driver IC. The resultant co-packaged solution ensures best-in-class DC precision and RF performance, and makes the

and makes the switch easy to use.

#### Dialog backs Energous for free space wireless charging by Nick Flaherty

ialog Semiconductor is backing a new entrant to wireless charging with a \$10m investment. Energous is the developer of WattUp, a new wireless charging technology that provides over-theair power at a distance. Alongside the \$10m investment in Energous, Dialog will be the exclusive component supplier of the WattUp chips while Energous use Dialog's

sales and distribution channels. WattUp uses RF frequencies to send power in a similar way to a Wi-Fi router and technology from startup Radient Micro-tech, and is a director of the AirFuel Alliance, which competes with the WirelessPower Consortium (WPC) that develops the Qi technology. The company raised \$20m earlier this year.

Like Radient, WattUp differs from inductive or resonant wireless charging systems in that it delivers power at a distance, to multiple devices, in any orientation, resulting in wire-free charging. It uses Dialog's SmartBond Bluetooth low energy solution as the out-of-band communications channel between the wireless transmitter and receiver and Dialog's power

management technology is then used to distribute power from the WattUp receiver IC to the rest of the device while Dialog's AC/DC Rapid Charge power conversion technology delivers power to the wireless transmitter.

WattUp uses small form factor antennas that are formed using the existing device's printed circuit board, removing the need for

# pulse

larger, more expensive coils used in competing solutions today. This enables broader adoption of wireless charging in a larger range of

battery-powered devices, such as smartphones, tablets, Internet of Things (IoT) devices, small form factor wearables, and Virtual Real-

ity (VR)/Augmented Reality (AR) devices. Energous hopes to tap Dialog's existing cutomers to grow the business.

#### 120A dual-phase DC/DC parallels up to 480A output

ricsson Power Modules' BMR467 is a two-phase 120A fully digital point-of-load (POL) DC/DC power module that, with four devices operating in parallel, can deliver a total of 480A, representing a power density of 15 A/ cm<sup>3</sup> (250 A/in<sup>3</sup>); its SIP package format measures 50.8 x 19.05 x 8.2 mm.

The converter's features include Automatic Digital Compensation and a half-load efficiency of 93.2% at 12 Vin, 1.8 Vout. Delivering 30A per module more than its pin-compatible predecessor BMR465, the BMR467 is also

compliant with the new 'teraAMP'

BMR467 120 A

AMP (Architects of Modern Power) specification. Ericsson's design is fully digital, that is, the internal control loop of the

converter is digital, which, among other benefits, Ericsson says delvers an efficiency curve that is flatter, and maximised, over more of

its load range. The unit is ready for future Software-Defined Power Architecture (SDPA) systems, anticipated as a path to efficient and energy-optimized net-

work architectures by 2020. The BMR467 POL converter can be operated as a standalone unit delivering 120A at output voltages from 0.6V to 1.8V, an output power up to 216W, as well as being part of a larger power system when processor boards require higher current. Built on a two-phase topology, the modules can become part of a multi-module and multiphase (up to eight-phase) power system that enables phase spreading, which reduces peak current and also the number of capacitors required by end systems. The module can be configured with support available via the downloadable Ericsson Power Designer software

tool.

#### 8-bit AVR MCUs gain PIC-style Core Independent Peripherals

ollowing its acquisition of Atmel, Microchip has announced a new generation of 8-bit tinyAVR

MCUs. From its PIC series, Microchip has applied the concept of core independent peripherals, that can exchange data without waking the main processor core, and implemented it in the tinyAVRs.

With this launch, Microchip says that it is reiterating both its intention to continue full support and

# pulse

development for both PIC and AVR architecture; and its focus on 8bit. 8bit MCUs continue to sell in ever-growing volumes, the company says, and remain an appropriate choice for very many simpler, especially real-time, tasks. The new series is supported by the START package (that generates 'housekeeping' code in C and frees development time for application coding) for graphi-

cal configuration of embedded software; it integrates rich features with 4 kB or 8 kB Flash in low pin-count packages; its core independent peripherals include a peripheral touch controller; and has self-programming for firmware upgrades and power-down mode with SRAM retention.

Four new devices range from 14 to 24 pins and 4 kB or 8 kB of Flash and are the first tinyAVR

microcontrollers to feature Core Independent Peripherals (CIPs). Microchip notes that Atmel had previously implemented a feature very similar to CIPs, in some of its larger MCUs – the Event system. With this series, it has effectively migrated that feature down to the smaller devices.

"This announcement is very important to Microchip as it represents the coming together of the two most powerful 8-bit MCU brands under one roof," said Steve Sanghi, CEO and Chairman of the Board of Microchip Technology Inc. "Customers love both PIC and AVR MCUs and Microchip is re-energising new product development to not only continue to support, but to grow the AVR portfolio."

Complete article, here

#### Programmable mixed-signal IC technology adds power switching, sequencing

Silego Technology has extended its GreenPAK programmable mixed-signal IC architecture

with a device that functions as a completely configurable and very small power management IC, with

functions including voltage monitoring, power sequencing, reset and integrated low-on-resistance power switching. Silego intends the SLG46125 to be the first in a series of

parts designed to create "Flexible Power Islands" (FPI). In products with complex, multi-rail power supplies – or even in designs with less complex needs - Silego believes that designers frequently need to create or retro-fit sections of the power distribution with specific characteristics, that may not be handled in a single central PMIC. In common with other Silego parts, the SLG46125 might be used from the outset in a design, or employed to apply a late design change. The device integrates dual 45 mΩ / 2A P-FET power switches.

Using FPIs, designers can divide their complex power system into some number of local power regions (or islands), each of which includes the power control, power sequencing and power regulation needed to support loads in the immediate vicinity. Silego believes this technique results in higher performance and a more efficient solution that can be flexibly tailored to the requirements of each individual system.

Complete

#### mmWAVE IMAGING

#### AIRPORT SECURITY SCREENING WITH MILLIMETRE WAVES

By Dr. Sherif Sayed Ahmed, Rohde & Schwarz

ully-automated personnel scanning using a multi-channel millimetre-wave array, with intelligent image-recognition algorithms that perform real-time analysis on raw data, can protect passengers' safety by identifying threats accurately and clearly, while also preserving travellers' privacy by eliminating any need to render images on-screen or store data.

### Introduction: stepping up airport security

Airport authorities responsible for preventing attackers boarding planes need an alternative to the basic metal detector gates now widely used at entrances and boarding points. Screening is time-consuming and imprecise, as the systems cannot determine the nature or exact location of a perceived threat. Every alarm must

be investigated further by a human operative, and many are found to be "false positives". Moreover, such equipment cannot detect non-metallic weapons such as explosives, in particular, which are a major concern for today's airline operators.

A fast and non-intrusive system is needed, which is able to "see through" clothes in order to detect concealed weapons or other proscribed items such as plastic explosives. Alternatives such as X-rays or ultrasound have a number of disadvantages: since X-rays have an ionising effect on body cells, some passengers – as well as security workers' representatives – may object to routine or repeated exposure. Ultrasound can only work at extremely close range using a coupling medium, such as a gel, which is obviously impractical in an airline scanning situation.

Scanning with millimetre waves offers an alternative. Some types of millimetre-wave scanners have already entered service in locations such as airports and public buildings. Unlike X-rays, millimetre waves have no ionising effect on organic tissue, and are not harmful to the human body. No physical contact with the body is needed to capture a 3D image, and the scan can be completed quickly to allow high throughput as is required in a busy airport scenario. However, some key challenges must be overcome.

#### **Design to preserve privacy**

Because millimetre waves do not penetrate the body, the image captured can present a detailed view of the surface of the body beneath clothing. Although this is ideal for de-

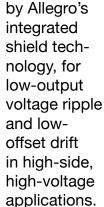

**Figure 1.** When the R&S QPS security scanner reports an alarm, the location of the object is marked on an avatar, a symbolic graphic of the human body. No image of the scanned body is seen or stored.

#### mmWAVE IMAGING

tecting almost any concealed object, including non-metallic weapons or explosive materials, there are obvious privacy concerns. Various initiatives have sought to address the issue: some authorities have introduced procedures to restrict the viewing and storage of captured images. However, the potential for breaches of such protocols to occur, or for misinformation about the handling of images to spread, could undermine confidence in the security systems that are intended to protect the travelling public. There is also the possibility for human error, when security staff are responsible for inspecting images individually at checkpoints, which may allow dangerous items to pass through.

Quick Personnel Security Scanner (R&S QPS) presents a technical solution to these challenges by completely automating the detection of concealed threats. No human-body images are presented on a screen for an operator to view, and no image data is stored. If a concealed object is detected, the system indicates its location on an avatar instead of displaying the passenger's own body (see Figure 1). Indicating the position of a suspect object in this way can help accelerate subsequent investigation, allowing harmless passengers to proceed quickly and those perceived as a threat to be detained confidently.

To achieve this, Rohde & Schwarz has intro-

duced important new technologies with the QPS that permit cost-effective full-body scanning and signal processing at near real-time performance.

#### **Technical choices**

Several alternative approaches are viable for millimetre-wave imaging. Passive systems can be effective for outdoor use, where the background is cool relative to the scanned object. However, in an indoor environment there is less contrast between background and object temperatures. For this reason, a system designed for use inside an airport has to use active illumination whereby a millimetre-wave signal of very low power is emitted towards the person [subject], and receiving units analyse the resulting complex patterns. Known techniques for millimetre-wave imaging with active illumination utilise either mechanical scanning, which is unable to support the fast cycle times needed for high-speed airport-security systems, or dense monostatic antenna arrays that employ large numbers of antennas, resulting in prohibitive high system cost.

The R&S QPS uses a new approach that clusters and positions multiple transmit and receive

antennas in a multistatic 2D array. Combined with digital beam-forming, these clusters create an electronically optimised aperture that allows a sparse and therefore low-cost antenna array to provide good image quality at close range. Close range imaging is optimal for human-body scanning due to the illumination limitations caused by the specular reflections out of the human skin at these frequencies. Thus long-range imaging is becoming impractical to find the small threats of interest.

In addition, the QPS is designed to operate at higher frequencies than conventional millimetre-wave systems. Operating in the 70-80 GHz frequency range allows higher signal bandwidth resulting in superior range resolution. Choosing this frequency range also allowed the development project to take advantage of design knowledge surrounding 77 GHz radar systems that is already established in the automotive industry.

In the continuation of this article, Dr Ahmed describes the antenna, signal generation and analysis chains that the test & measurement company created to address this alternative measurement domain – click for pdf.

Download PDF of Article

Find mmWave imaging on EETsearch

# **Analog Tips**

#### ADC INPUT IMPEDANCE MATCHING BY IAN BEAVERS

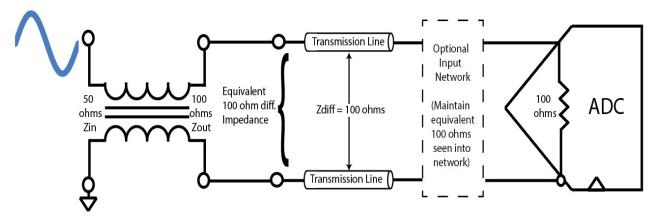

The differential input to an ADC often originates as a single-ended signal from an antenna or other signal acquisition component. Before the signal can be delivered to the ADC, it must be converted to differential by an active device such as an amplifier, or a passive device such as a balun or transformer. In either case, the impedance matching within the path is critical to ensure that signal power is neither lost nor reflected back to the source.

First, it is important to understand the ADC's input impedance. Most high speed ADCs will have an input impedance of  $50~\Omega$  or  $100~\Omega$ , although other values are possible. The second factor is the output impedance of the device that drives the ADC. Ideally, the output impedance of this device should match the input impedance of the ADC, but this is not always possible. Third, the characteristic impedance of the transmission line between these components should match on both ends.

Sometimes, a passive input network is needed ahead of the ADC to create a matched termination

impedance or to attenuate the signal. Care should be taken to calculate the discrete impedance values so the lumped equivalent network. when considering the ADC, matches the output impedance of the balun or amplifier. Passive component tolerances and parasitic effects should not be neglected as potential sources of imbalance.

While not an explicit component, matching the transmission line from the upstream signal source to the termination impedance at the ADC is equally critical. The characteristic impedance of the differential transmission line formed by the PCB traces must be maintained throughout, and must

match the termination impedance. If the transmission line with Z0 is terminated into impedance less

a reflection with the same polarity back to the source.

**Figure 1.** Maintain a matched transmission line from the source to the ADC by carefully selecting the same impedance within active components and passive devices for any optional input network.

than Z0, there will be a reflection with opposite polarity back to the source. If the transmission line with Z0 is terminated into impedance greater than Z0, there will be In this example, a  $100-\Omega$  differential transmission line must match the  $100-\Omega$  ADC termination impedance and the  $100-\Omega$  output impedance of the passive balun.

**lan Beavers** [ian.beavers@analog.com], a staff engineer for the Digital Video Processing Group at Analog Devices (Greensboro, NC), is a team leader for HDMI and other video interface products. With over 15 years' experience in the semiconductor industry, he has worked for ADI.

#### **DESIGN TOOLS**

#### OPTIMIZED FOR ADAS APPLICATIONS: NEW COMPILER CHALLENGES - PART 2

By Dr. Alexander Herz, Tasking

The compiler is a key tool for the cost-efficient design of ADAS applications. However, the tools currently available must be better adapted to this challenging task. This includes considering the code structures and specific safety requirements typical of ADAS applications.

When planning a compiler technology roadmap, you will inevitably touch the issue of advanced driver assistance systems (ADAS), which all major OEMs and software suppliers of the automotive industry are committed to. A closer look, though, will raise some questions: What requirements are placed on compilers and toolsets by ADAS applications? Are these things related at all? What are the differences between traditional automotive applications and ADAS applications?

In part 1 of this article, Dr. Herz looked at the challenges posed by ADAS applications; defining suitable architectures; code structures; and the problem of parallelisation. The article continues here; click the link below for a pdf of the complete article.

#### Hardware accelerator support

Intrinsics are the most straightforward method to support hardware accelerators. These constructs

can be used to address special hardware instructions from C/C++. At the next level, special high-level languages, most of which are similar to C, are supplied enabling designers to address their hardware efficiently. Although these high-level languages require compilation and optimization. their closeness to the underlying hardware simplifies the whole process (OpenCL for

NVIDIA, compiler from NVIDIA; C for GTM, compiler from TASKING; extended C for EVE from TI). As a final option, compilers can automatically detect code areas that can be executed efficiently by an accelerator in order to automatically generate the appropriate code (SIMD, icc). However, this fully automatic discovery is restricted in most cases because standard C/C++ code is not explicitly written for the specific accelerator. Quite often, minor code modifications yield excellent results, although a suitable tuning tool is indispensable in

input layer 1 hidden layer 2

Figure 3. Schematic diagram of a neural network

order to find and implement the necessary changes with reasonable overhead.

Furthermore, many heterogeneous hardware architectures mandate that each programmable unit be addressed with its own compiler. In order to avoid dealing with an excessive number of incompatible tools, which would generate new safety risks, it is advisable to use tool environments that can address all programmable units and ensure mutual compatibility between the tools.

#### **DESIGN TOOLS**

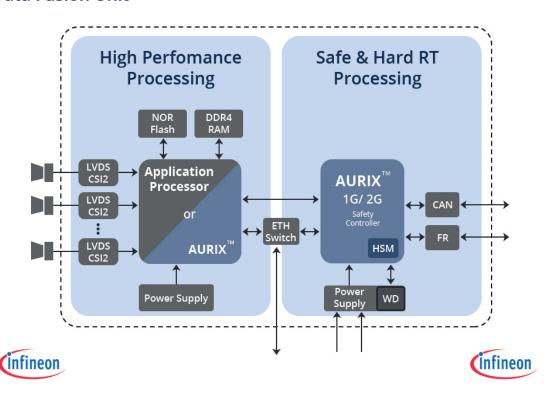

For instance, the TASKING tool environment for Aurix (Infineon) can be used to program and debug all units of the architecture from a single IDE. Interactions between units can be controlled and monitored more safely because symbol information is compatible between the different units.

### Safety requirements for ADAS applications

In order to meet the specific safety requirements of ADAS applications, tools (modelling tools, compilers, analysis tools) and software components (OSs, libraries, etc.) relevant for these applications must be developed and qualified according to ISO 26262.

Some of the newer safety requirements can be understood using neural networks (Figure 3). Neural networks are software components that are often used for detecting and processing sensor data in ADAS applications. Although there are interesting prototypes based on neural networks, it is still not clear how a correct behaviour of these networks can be ensured in extreme situations.

At the moment, no known procedure can guarantee that neural networks always behave correctly without any risks for road users. Therefore, one cannot let neural networks make safety-critical decisions without a suitable supervisory entity. In addition to the hardware for the neural networks themselves, which will issue a hard-to-predict

decision proposal based on the input data (e. g. accelerate to 100 km/h. pass on the left side, actuate an emergency stop, etc.), there must be a supervisory entity running on hardware featuring the highest safety certification (ASIL-D). The latter will operate using predictable algorithms to check if the proposal made by the neural networks can be executed safely or if a

#### **Data Fusion Unit**

**Figure 4.** High-performance processing for neural networks and image processing combined with safe processing for the supervisory entity

safer alternative should be chosen (Figure 4). For instance, the supervisory entity would check if the passing manoeuvre proposed by the neural networks can be executed without any risk. For this purpose, it will use its own, predictable calculations to check if there are no obstacles etc. Predictable algorithms are still being researched in some areas

(e.g. data fusion) in order to create an effective supervisory entity.

Many of the predictable algorithms for ADAS applications are based on linear algebraic calculations supported by LAPACK and others. Optimized solutions including the LAPACK

#### **DESIGN TOOLS**

Performance Libraries from TASKING can be used to implement these algorithms efficiently and safely on various target platforms.

The remaining parts of ADAS applications can be certified using several tools and processes that are helpful to meet various ISO 26262 requirements. Simple programming errors (including non-initialized data) can be detected efficiently using static analysis (Polyspace, Klocwork, etc.). For detection of safety relevant access violations (software components with different ASILs accessing each other and creating protection faults in the Memory Protection Unit - MPU), it is beneficial to use the TASKING compiler with its associated safety checker tool support. The compiler's integrated safety checker extension can be used to define different safety categories (e. g. ASIL A to D), to assign data and functions used in the project to different safety categories and to manage the access privileges between these categories.

This information can then be used for two purposes. First, the compiler is unable to perform certain optimizations (reverse inlining, code compaction) because these optimizations could result in safety access violations if they are performed without taking the access privileges into

account. Second, the same information can be used with the TASKING safety checker tool (which can also be obtained for third party compilers, if desired) to identify undetected access violations that would generate MPU exceptions without any additional testing overhead and with high code coverage.

In order to qualify the tools (modelling tools, compilers, static analysis, safety checker, etc.) according to ISO 26262, most manufacturers provide an ISO Kit greatly simplifying the necessary process. In this context, it is helpful to work with tools and manufacturers with a long track record in the automotive area. ISO 26262-8 uses the term 'proven in use' for this purpose: it is assumed that a tool that was frequently used over a long time with few problems will probably be less fault-prone than a new one.

Apart from addressing the safety risks outlined above, the compiler and its associated tools can help to mitigate the design risks associated with ADAS applications.

Dr. Herz concludes Part 2 of this article with a section on controlling design risks; click for pdf download.

Download PDF of Article

Find Compilers for ADAS on EETsearch

**LEDLighting**

EDN Europe December 2016

#### **RF ENERGY**

#### HOW GAN IS TRANSFORMING RF ENERGY AND COOKING APPLICATIONS

By Mike Ziehl and Mark Murphy, MACOM

The RF energy market has evolved relatively slowly since magnetrons first came into widespread commercial use in microwave ovens in the early 1970s. Today, there exists a variety of use cases for RF energy, including industrial and consumer cooking, drying, lighting, medical, and automotive applications.

Recently, solid-state technology has appeared on the scene as a viable replacement and enhancement for magnetrons as the heating engine, delivering several key advantages: longer lifetime, enhanced reliability, precise power level and energy direction control, increased efficiency, and smaller dimensions.

#### Price and efficiency inhibiting growth

While the RF energy market is widely predicted to grow to as much as a billion dollars over the next five years, its expansion so far has been inhibited by solid-state technology limitations.

To reduce energy consumption requires high efficiency, less cooling or dissipated power heat sinking, which is an important consideration in all RF energy application designs. Ruggedness is critical for the harsh operating environments and unpredictable loads that the heating element is faced with during operation which, combined with the need for consistent power and long operating

life, represents a huge disadvantage for existing magnetron technologies.

To date, the only solid state technology that has come close to the sector's tough cost targets has been silicon LDMOS. Driven by developments for basestations, LDMOS technology is well established with a competitive cost structure and volume supply chain. However, it falls short on efficiency (by more than 10%), ruggedness (due to lower breakdown voltage and lower operating temperature), and power density (which is only one-quarter to one-sixth of GaN).

GaN-on-SiC (gallium nitride on silicon carbide) can meet the necessary performance but has been unable to meet the necessary manufacturing scale and cost structure, and has traditionally been 5 to 10 times more expensive than legacy technologies – the physics of growing silicon carbide substrates is truly cost prohibitive even at large economies of scale.

However, as GaN transitions from traditional 4-inch compound semiconductor wafer fabs to 6-inch and 8-inch silicon fabs over the coming year, GaN-on-Si is starting to break through the cost threshold towards the ultimate goal set by the RF Energy Alliance of 5 cents per Watt, meaning that designers can finally move forward with mainstream deployment. For example, MACOM offers a

300W GaN-on-silicon device in plastic packaging that sells at around \$15 and delivers over 70% efficiency. This level of price to performance has simply not been attainable until now.

#### RF energy in cooking applications

One of the largest potential RF energy markets today is found in RF cooking and heating applications. Well over 70 million microwave ovens are manufactured annually, spanning low-cost consumer grade to high-end professional and industrial ovens.

RF power transistors offer numerous performance advantages over traditional magnetrons, including better control of the cooking process through greater precision in setting the power level and RF energy direction inside the oven.

Today's microwave ovens lack effective control of the power level or the ability to direct the energy where required, which results in hot spots and overcooking.

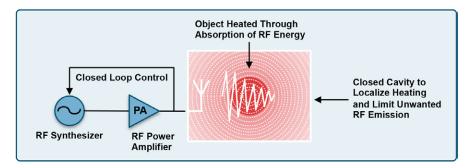

In the case of solid state devices, the frequency, amplitude, phase, pulse width and modulation can all be accurately controlled. With closed-loop control between the RF power amplifier and the RF synthesizer, a feedback loop enables the assessment of forward and reflected power levels, hence facilitating accurate and optimised control of

#### RF ENERGY

RF Small Signal RF & Data To System **High Power Generation &** ➤ RF Out Controller **Amplifier** Control **Heat Sink Power Supply**

with a microcontroller

- Power supply

Figure 1. Solid-state powered RF energy application

Figure 2. Block diagram of a solid-state RF generator system

following:

the energy pattern.

This means that with three or four transistors and antennae, it is possible to direct the energy exactly to where it is required on the food, whilst the reflection and absorption of the radiation can be accurately measured. This feedback loop and the accurate control enabled by solid state transistors, enables an oven to accurately determine how well the food is cooked, and thus achieve reproducible results.

Varying the phase between multiple antennae can enable the field distribution inside the oven to be intelligently controlled to achieve homogeneous cooking results. Furthermore, by modifying the frequency and phase to match the food in the oven. very high RF energy delivery efficiency can be attained - above 90% even for small loads. It has been demonstrated how a steak can be cooked on the same plate as ice cream without it melting, showing the precision of the directed RF energy. In practice, one gets outstanding

control over internal meat temperature, with a tight tolerance of just one degree Celsius. Therefore, food can be cooked automatically, and one simply specifies the steak "doneness" level, for example, medium rare: and the oven will measure the food's properties and calculate the required settings. Without having to manually enter the power levels, cooking is more predictable, and the interface more user-friendly.

As well as convenience, precise temperature control means that the cooked food is healthier and retains more of its nutrient content than is the case with traditional microwave ovens. The result is no more over-cooking or hotspots destroying nutrients and amino acid chains.

#### The solid state subsystem

For this kind of microwave oven application, a solid

**Download PDF**

of Article

In the continuation of this article, the authors further explore issues of performance, reliability, lifetime and overall cost-competitiveness in moving to a GaN energy source. Click for pdf.

Find GaN-on-Si power transistors on EETsearch

state RF generator subsystem could consist of the

- Small-signal generator, which may be co-located

- High power amplifier connected to a heat sink

A block diagram for this system is shown above.

applicator, which may be a cavity or an otherwise

confined environment. This contains the food absorbing the RF radiation and provides the

The "RF Out" connection leads into an RF

required level of EMC shielding.

**EDN Europe** December 2016

www.edn-europe.com

# EMBEDDED SYSTEMS

#### 7 TIPS FOR OPTIMIZING EMBEDDED SOFTWARE

BY JACOB BENINGO

n an earlier column, I discussed key embedded system characteristics that in many cases require optimization. These characteristics include system timing, code size, RAM usage, and energy consumption. While optimizing each characteristic typically requires its own methods and techniques, there are several general tips developers can follow when optimizing their embedded software.

### Tip No. 1 – Always create a baseline for comparison

Creating a baseline to compare optimization results against is obvious, and yet it would surprise you how many times I encounter teams in a hurry that jump straight into optimizing without any baseline. A baseline measurement is important because there are diminishing returns with each optimization cycle. For example, a first pass at optimizing for energy may result in a 20% improvement. The second, 10%, then 5%, and so on. Developers need to be able to see this trend and quantify the improvement they are seeing in the system as a function of their time input.

#### Tip No. 2 – Set an optimization target

Each optimization pass requires more and more time to squeeze just the smallest improvement from the system. Teams need to carefully balance their time investment and determine if the resultant improvement is worth the time. Simply trying to go as low as you can go can become addicting. Before one realizes it, one can be spending weeks optimizing a system that no longer needs to be optimized. Before optimization begins, then, teams should set a target level that -- once achieved -- is good enough for the current application. Achieving that target indicates that the optimization process has completed.

### Tip No. 3 – Get the right tools to make measurements

Optimizing a system can be extremely difficult without the right measurements tools. Optimizing for energy, for instance, can't be done if there is not an accurate means to measure the system and microcontroller energy draws. In many cases I'll see teams fail to separate these two different energy measurements and attempt to minimize microcontroller energy when it can't go any lower.

Developers interested in optimizing for performance might find the Segger System View Utility, that I wrote about in Hands-on: Segger System View Utility, to be critical to understand which functions are monopolizing the CPU. Without tools that can accurately measure or allow a developer to peer into the system behaviour, there is no point in attempting to optimize a system.

#### Tip No. 4 – Use optimization tools

There are many areas of embedded software that can be optimized in order to decrease code size or improve performance. In some circumstances there are separate or add-on toolchains that can perform the optimizations. An example optimization tool is the Somnium DRT optimizer that can be used with GCC to optimize code size, energy usage, and performance.

Sometimes external tools may not be necessary, though. Just selection of the right toolchain may be sufficient. I recently wrote about Open Source versus Commercial Compilers where I explored the fact that in Coremark tests, under the same test conditions with the same microcontrollers, commercial compilers generated higher scores when compared with open source compilers such as GCC.

### Tip No. 5 – Use compiler attributes and #pragma

In general, I strongly dislike using #pragmas or compiler attributes. Attributes and #pragmas are generally non-portable and changing compilers can result in software bugs. However, when it comes to fine tuning embedded software, developers will usually not have a choice. Using attributes and #pragma can improve speed, selectively apply

# EMBEDDED SYSTEMS

optimization to a single function, and so forth. So for those reasons, developers intent on optimizing software should get familiar with attributes, but also read Writing Portable Optimizations in C so that they can understand how to write optimizations that are still portable and won't come back to bite them.

### Tip No. 6 – Don't hesitate to experiment

There is no set-in-stone practice for optimizing a system and developers shouldn't feel constrained to follow any specific technique. Sometimes the best way to learn and optimize a system is to put together experiments and just see what happens. When I first started optimizing systems for low power, there was a lot of trial and error associated with it. However, through experimentation and recording results, I was able to figure out what works, what doesn't, and what is a waste of resources and time. A simple example is given in how to Make the most of printf. Through trying different driver models there are ways to drastically improve the real-time performance a developer gets when using printf, which is usually assumed to be far better than it really is.

#### Tip No. 7 – Dig into the compilergenerated instructions

In applications that are extremely resource constrained, there comes a time when developers just need to roll up their sleeves and dig into the compiler-generated instructions. Selecting the

ternary operator over an if/else could potentially be the difference between three or four extra instructions being executed, which causes the application to implode. While languages such as C are standard, each compiler optimizes and generates the machine instructions slightly differently. The only real way to know what your compiler is doing is to review the assembly. (Checkout Ternary Operator versus if/else If you are interested in a low level look).

#### Conclusion

Applications will drastically vary on their optimization needs. Some applications that are in low volume production may require no optimization at all. In others, where every clock cycle or nanoamp matters, a vast amount of time may be spent trying to squeeze every last drop of performance or energy from the system. While each system is different, these tips provide developers and teams with a starting point that can get them on the road to a more efficient system.

Jacob Beningo is an embedded software consultant who currently works with clients in more than a dozen countries to dramatically transform their businesses by improving product quality, cost and time to market. He has published more than 200 articles on embedded software development techniques, is a sought-after speaker and technical trainer and holds three degrees which include a Masters of Engineering from the University of Michigan. Feel free to contact him at jacob@beningo.com, at his website www.beningo.com, and sign-up for his monthly Embedded Bytes Newsletter here.

#### SUPERCAPACITOR MANAGEMENT

#### LOW COST AND LOW DROP-OUT LINEAR AND SWITCHED-MODE SUPERCAP CHARGERS

By Dan Tooth, Texas Instruments

When the mains power fails, supercapacitors can provide back-up power to maintain system functionality for a period of time. The supercapacitor or "supercap" needs to be charged and how fast that charging should be is determined by the system requirements and leads to the choice of either a low current linear charger, or a switched-mode charger - should a fast re-charge time be required. This article looks at both types with an emphasis on both low drop-out, such as is the case when a 5V source is charging a 5.4V-rated supercap; and on low cost.

#### Supercap application

The application of interest is Smart e-Metering and has a high supercap discharge current, such as presented by a GSM/GPRS load, with an average load current of 500 mA being typical. This calls for a low ESR (equivalent series resistance) supercap and the device used for testing was a Cooper Bussmann PHV-5R4V255-R, which is a 5.4V(max), 2.5F, 75 m $\Omega$  device. The 5.4V rating applies at 65°C max and is linearly de-rated to 4V at 85°C. This supercap is a two-terminal device and will consist of two matched supercaps placed internally in series, to achieve the 5.4V rating.

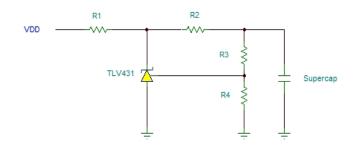

#### **Resistor charger**

Figure 1 shows a simple supercap charger, which uses a resistor to charge the supercap. A TLV431 (or TL431) is present to clamp the voltage across the supercap to the desired level to prevent over-charging. Note that the clamp voltages of these devices when fully "on" are ~1V and ~2V respectively. The charge current is a maximum when the supercap is uncharged and decays exponentially towards zero as the supercap charges up towards the charging source voltage. The designer has to juggle the desired re-charge time (charge current) with the power dissipation in the resistor, which is at a maximum when the supercap is uncharged. The charge time is given by;

$$t = -RC \ln(1 - V_{C}/V_{DD})$$

where  $V_{\text{DD}}$  is the charging source voltage,  $V_{\text{C}}$  is the voltage across C, the supercapacitance, and R is the resistance through which it is being charged. The influence of the voltage divider across the supercap is ignored as it is a much larger resistance than the charging resistances.

For example, in Figure 1 then  $V_{DD}$  is a 5V charging source and the desired charge voltage across the supercap is set at 4V, which is the maximum value

**Figure 1.** Resistor charger with TLV431 overvoltage clamp

for this Bussmann supercap at  $85^{\circ}$ C. If R1 =  $110\Omega$  and R2 =  $25\Omega$  then the initial charge current is  $5V/135\Omega=37$  mA and the charge time is approximately 9 minutes. The charging resistance is split into R1 and R2 to provide some protection discharge resistance should the supercap discharge back through the TLV431. The TLV431 starts to conduct when its REF pin reaches 1.24V, which occurs at a supercap voltage of 4V given R3 = 6k and R4 = 2k7. When the supercap is fully charged, the TLV431 is shunting  $(5V-4V)/110\Omega=9$  mA to GND.

#### Constant current source charger

To maintain the charging current constant throughout so as to charge the supercap faster, then another approach is to use a constant current source. The time taken to charge the supercap is

#### SUPERCAPACITOR MANAGEMENT

$t = C.V_C / I$

where I is the constant charging current. The reduced charging-time benefit of the constant current charger is not that significant if the source voltage V<sub>pp</sub> and final capacitor voltage V<sub>p</sub> are signigficantly different. For example, to charge a 2.5F supercap to 50%  $V_{DD}$  and keep the power dissipation in the charging resistor to 0.5W then a  $50\Omega$  resistor is used and the charge time is ~87 seconds. If a constant 100 mA current source is used instead, then the initial power dissipated is also 0.5W but the charging time is only reduced to be 62 seconds. If, on the other hand, the goal is to charge the supercap to 95%  $V_{DD}$ , then the charging resistor method will take more than 6 minutes, versus 2 minutes for the constant current source. The conclusion of this is that if the  $V_{pp}$  and desired V<sub>c</sub> are similar, then a current source will charge the supercap much faster for the same peak power dissipation.

The technique used to achieve the current source here is to make use of an IC (TPS75100) that was designed to drive a constant current into LEDs. It has a low drop-out of ~100 mV at 15 mA, per channel. The IC is split into two banks of two current sources per bank (i.e. four current-source "channels" in total), each bank being controlled by its own enable pin. The constant current per channel is set by a programming resistor on the  $I_{\rm SET}$  pin. Up to 25 mA can be sourced per channel

and channels can be paralleled, to give up to a 100 mA current source if all four are paralleled together to drive a common load. TPS75100 (and TPS75105) are available in a QFN package with a power pad to dissipate the power. If the resistor on  $I_{\text{SET}}$  is unpopulated then the IC defaults to a fixed current per channel, which for TPS75100 is 10 mA and for TPS75105 is 5 mA. For an uncharged supercap, then the initial output voltage is 0V and the accuracy of the TPS75100 current source is worse, being ~12% tolerance, shown in Figure 12 of the datasheet and reaching specified tolerance (4% max) when the supercap voltage has risen to > 1.25V.

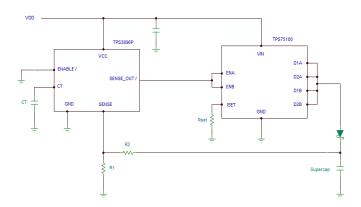

**Figure 2.** TPS75100 charger, using TPS3896P as over voltage protection

Figure 2 shows the implementation using TPS75100. TPS3896P is also used to regulate the desired voltage across the supercap. TPS3896P is only necessary should the input source voltage be greater than the max charge voltage of the supercap. TPS3896P is a voltage supervisor and when the voltage on its SENSE pin is ≥0.5V, it pulls its SENSE\_OUT/ pin low for a delay time set by the capacitor on the CT pin. The delay provides a minimum on-time to prevent the TPS75100 being enabled/disabled too quickly.

For charging supercaps from a higher input voltage source then TPS7B7701-Q1 could be used. This has an accurate, programmable current limit and it also blocks reverse current flow. It is a linear regulator and the final charge voltage (output voltage) can easily be set. It also has various fault reporting features.

In the conclusion of this article, the author adds a switch-mode DC/DC charger to the options, and presents measured results from the circuits described – click for pdf.

Download PDF of Article

Find Supercapacitor chargers on EETsearch

#### **CUSTOM SOCS**

#### AVOIDING THE ASIC VS FPGA GAMBLE; SMART ENGINEERING REQUIRES SMART SOC DESIGN

By Patrick Osterloh, Toshiba Electronics Europe

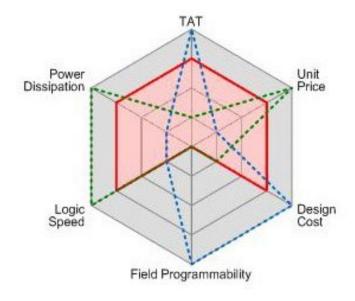

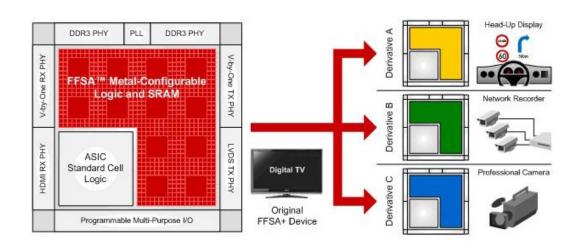

System on Chip (SoC) integration holds the key to delivering the smart and connected systems that are needed to manage life in the future, from autonomous driving to intelligent factories, and from advanced medical technology to consumer IoT devices. In many of these systems, an optimized SoC will be critical for delivering the advanced functionality, performance and connectivity required within tight size and power constraints – and at the right price.

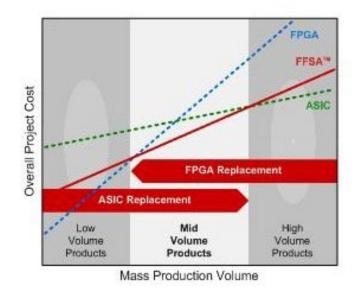

Traditionally, designers have been presented with a choice of implementing their SoC as an ASIC, if the projected volumes have been high enough to amortise the relatively high design costs, or to use an FPGA if anticipated production volumes are lower. An FPGA can impose somewhat higher power consumption and greater cost per unit, in exchange for lower design costs and engineering risk.

Now, however, these relatively straightforward choices have become more complex. While on the one hand growing competition means it is tougher to achieve the large market share needed to justify high production volumes, the latest process nodes drive up the

Figure 1. FFSA, ASIC, FPGA comparison (red, green and blue profiles)

minimum volume at which an ASIC project becomes viable. Obvious project risks of an ASIC solution arise from the possibility that a product is not as successful as anticipated, or that logic changes would require an expensive re-spin.